CPU

Introducción

La evolución de las CPUs ha supuesto un continuo incremento de potencia de cálculo al tiempo que se han reducido considerablemente los costes de fabricación, el tamaño que ocupan y la cantidad de energía que consumen.

La siguiente tabla muestra las características de algunos microprocesadores famosos:

| año | marca | modelo | transistores | f. reloj | bits | tipo |

|---|---|---|---|---|---|---|

| 1971 |

Intel | 4004 | 2300 | 740KHz |

4 |

CISC |

| 1976 |

Zilog |

Z80 |

2.5MHz |

8 |

CISC |

|

| 1978 | Intel | 8086/8088 | 4.7MHz | 16 | CISC | |

| 1979 | Motorola | 68000 | 68000 | 8MHz | 16/32 | CISC |

| 1992 |

Digital |

Alpha |

2.85 millones |

200MHz |

64 |

RISC |

| 1993 | Intel | Pentium |

3.1 millones |

60MHz |

32 | CISC |

| 1999 | Motorola | PowerPC G4 |

10.5 millones |

450MHz | 32/64 | RISC |

| 2001 |

Sun |

UltraSPARC III |

29 millones |

600MHz |

64 |

RISC |

| 2005 |

IBM, Sony, Toshiba |

Cell |

234 millones |

4.8GHz |

64 |

RISC |

Las capacidades de las CPUs han aumentado gracias a que la tecnologia cada vez puede implementar un número mayor de transistores en el área relativamente pequeña que utiliza un circuito integrado (die size). En un circuito integrado la mayor parte del volumen está consumido por el encapsulado que proporciona los conectores (pins). Realmente el área en el que está implementada la lógica del circuito es mucho menor.

El tamaño máximo del circuito integrado está limitado por la velocidad de reloj de funcionamiento, no es posible construir circuitos grandes que funcionen a velocidades elevadas. Otro problema inherente al diseño de microprocesadores es el del consumo y la disipación de calor. Integrar un mayor número de transistores y subir la frecuencia de funcionamiento genera una mayor cantidad de calor. Como el calor se produce en un área pequeña, es muy importante (y en ocasiones muy difícil) disipar el calor hacia el exterior.

Características de un µP

Características físicas:

- Encapsulado:

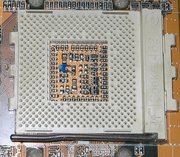

- La función del encapsulado es proteger al circuito integrado y proporcionar los conectores que permiten utilizarlo. Existen diferentes tipos de encapsulados: DIP (Dual Inline Package), PGA (Pin Grid Array) y FCPGA (Flip Chip Pin Grid Array).

En el diseño del encapsulado se tiene en cuenta el calor que se deberá disipar durante el funcionamiento del µP. Por eso, normalmente la parte superior es metálica y lisa, para permitir un buen contacto y una buena transferencia de calor hacia el disipador. - Zócalo (socket) utilizado:

- Normalmente el µP no está soldado al circuito impreso (placa base), se utiliza un zócalo (socket) que permite reemplazar, por avería o por actualización, el µP. Dado el gran número de pins que tienen los µP actuales, algunas veces es necesaria mucha fuerza para insertar/extraer el µP del zócalo, por eso se han diseñado zócalos especiales como el ZIF (Zero Insertion Force), que utilizan una palanca para liberar los contactos de manera que el µP se pueda insertar/extraer con facilidad. Una vez que se ha colocado el µP en el zócalo, debe retornarse la palanca a la posición en la que fija los pins del µP.

- Características eléctricas:

- En su contínuo intento por evitar el calor, y por reducir el consumo energético, los µP han reducido su tensión de alimentación de manera contínua. En general puede asegurarse que la cantidad de calor generada depende de: la frecuencia de funcionamiento, el número de transistores, la tensión de alimentación.

En los dispositivos portátiles/móviles es especialmente importante limitar el consumo y el calor generado a fin de prolongar al máximo la autonomia de las baterias.

En el caso de la arquitectura SPARC, los primeros micros (1992 microSPARC I) funcionaban con una tensión de alimentación de 5V, un reloj de 50MHz, contenian 0.8 milones de transistores y consumian 2.5W. Los últimos modelos (2005 UltraSPARC IV+) han reducido su tensión de alimentación a 1.1V, utilizan un reloj de 1.5GHz, contienen 295 millones de transistores y consumen 90W.

Arquitectura CISC/RISC:

- CISC (Complex Instruction Set Computer): Ordenador con juego de instrucciones complejo

- RISC (Reduced Instruction Set Computer): Ordenador con juego de instrucciones reducido

Los acrónimos CISC/RISC centran sus diferencias en el juego de instrucciones (aunque hay otros aspectos que distinguen a estas arquitecturas).

El juego de instrucciones es el conjunto de operaciones que la CPU puede realizar. Estas operaciones pueden ser relativamente básicas (como en la arquitectura RISC): cargar un registro, guardar un registro en memoria, realizar una suma, una resta, un desplazamiento o una operación lógica. O más complejas (como en la arquitectura CISC): realizar operaciones aritméticas/lógicas con datos que se encuentran en memoria principal, realizar no sólo sumas y restas sinó también divisiones y otras operaciones aritméticas complejas.

En la arquitectura RISC se utilizan varias instrucciones sencillas para conseguir un resultado equivalente al de las instrucciones CISC más complejas.

| RISC | cisc | |

|---|---|---|

| Juego de instrucciones: |

Instrucciones básicas. |

Instrucciones básicas e instrucciones complejas. |

| Ciclos por instrucción: |

Normalmente 1 |

Normalmente varios. Si la instrucción es compleja muchos. |

| Banco de registros: |

Grande | Limitado |

| Frec. de trabajo: |

Es más fácil aumentarla |

Difil de aumentar |

La filosofía RISC demuestra que en un programa real las instrucciones que se utilizan con mayor frecuencia son siempre las mismas. Las instrucciones más complejas se utilizan muy raramente, por eso, es un acierto dedicar transistores a optimizar las tareas más comunes, aunque eso implique que para realizar un paso más complejo se deba realizar más de un paso pequeño.

Segmentación o pipeline

La segmentación consiste en descomponer cada instrucción en una serie de etapas independientes, de manera que dos o más instrucciones puedan estar en ejecución simultáneamente.

La segmentación se inspira en una cadena de montaje. En una cadena de montaje los pasos se realizan secuencialmente, si por ejemplo se fabrican coches, en la cadena habrá diferentes coches en construcción.

Es posible que el tiempo total de construcción de un coche sea de 12H, sin embargo, es posible que (ya que en la cadena se están construyendo varios coches simultáneamente) cada 5 minutos salga un coche nuevo de la cadena.

De este modo, en una CPU moderna mientras se ejecuta una instrucción es posible que se esté accediendo a memoria para recuperar la próxima instrucción. Dos instrucciones pueden ejecutarse simultáneamente si no utilizan las mismas unidades de ejecución en la CPU.

CPU Superescalar

Una CPU es superescalar si cuenta con varias unidades de ejecución. Por ejemplo tiene una ALU con dos sumadores, de manera que se pueden realizar dos sumas a la vez. A este tipo de ejecución se le denomina ejecución paralela.

Aunque algunas unidades de ejecución estén duplicadas, no siempre es posible tener a todas trabajando. Puede ser que para realizar una operación se deba conocer primero el resultado de una operación anterior. Así, hasta que no acabe la primera operación no se podrá realizar la siguiente (aunque haya unidades de ejecución disponibles).

La arquitectura VLIW puede considerarse un tipo de computación superescalar estática, pues la planificación sobre el uso de las unidades de ejecución no se realiza dinámicamente en el µP sino en tiempo de compilación.

Máquinas vectoriales

En una máquina escalar realizar 30 sumas requiere ejecutar 30 veces una instrucción suma sobre los datos adecuados. En una máquina vectorial es posible realizar una suma sobre un conjunto de datos. De este modo, cargar una sola operación (la suma) puede dar trabajo a varias unidades de ejecución (todos los sumadores).

Una máquina puede ser vectorial respecto al código, respecto a los datos o respecto a ambos, de este modo surgen cuatro tipos diferentes:

| Una instrucción | Varias instrucciones |

|

|---|---|---|

| Un dato |

SISD | MISD |

| Varios datos |

SIMD | MIMD |

De estas tecnologias, la que ha tenido mayor aceptación en el mercado de consumo es SIMD (Single Instruction Multiple Data) que es capaz de aplicar la misma instrucción sobre un conjunto de datos. Su utilidad radica en que en las operaciones multimedia (con audio o vídeo) es muy frecuente tener que realizar una misma operación sobre un conjunto grande de datos.

En el caso de Intel se ha extendido el juego de instrucciones de la arquitectura x86 con las instrucciones mmx, sse (La implementación de AMD se llama 3DNow!) y en el caso de los µP PowerPC se han incluido las instrucciones AltiVec. Todas estas instrucciones son SIMD.

Memoria Cache

La velocidad de funcionamiento de un µP es mucho mayor que la velocidad de funcionamiento de la memoria principal. Traer y llevar datos entre ambos elementos consume un tiempo valioso. Se intenta que la CPU siempre tenga a su disposición los datos con los que ha de trabajar. Una manera de conseguirlo es utilizar una memoria caché que almacena la última información con la que ha estado trabajando la CPU.

La memoria caché es más rápida que la memoria principal (y también tiene una capacidad mucho más limitada). Normalmente en la memoria caché se definen espacios de almacenamiento diferenciado para los datos y las instrucciones. A este diseño se le llama Arquitectura Harvard.

Dos tipos de memoria caché:

- Escritura inmediata (write through)

- Cuando se modifica un dato en la caché, inmediatamente se actualiza la memoria principal.

- Escritura aplazada (write back)

- Cuando se modifica un dato en la caché, se marca como sucio (se utiliza el bit dirty). De este modo queda claro que al reemplazar el dato de la caché será necesario actualizar la memoria principal.

Otras optimizaciones:

Muchos de los µP actuales implementan:

- Ejecución fuera de orden (Out of order execution):

- En la CPU no se ejecutan las instrucciones en el órden en el que están programadas, sinó a medida que están disponibles los operandos que necesitan. De este modo se intenta evitar los ciclos de CPU perdidos en espera de los operandos. Es una optimización difícil de implementar.

- Predicción de saltos (Branch prediction):

- Cuando durante la ejecución de un programa se realiza un salto se pierde tiempo, porque:

- La información de la caché de datos/instrucciones se puede quedar obsoleta

- No se han precargado las instrucciones a ejecutar